Description

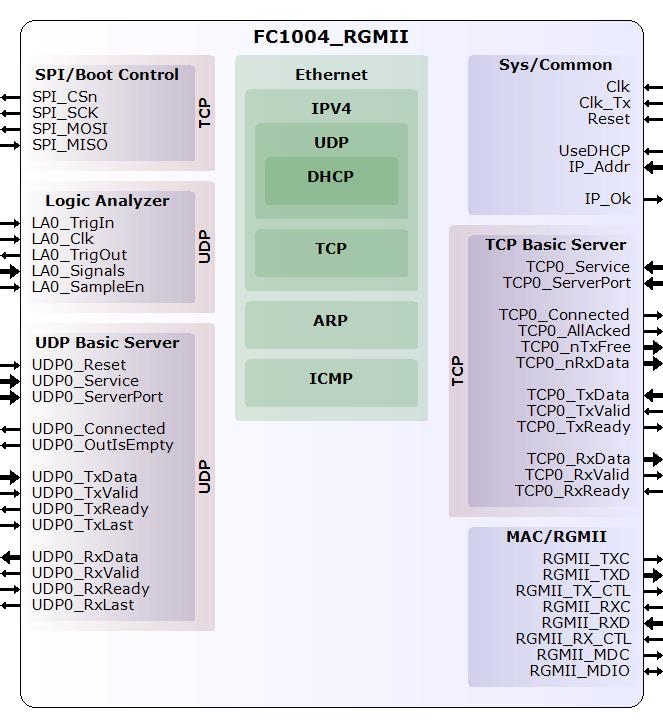

FC1004_RGMII supports RGMII gigabit Ethernet PHY interface. The core contains functions for remote SPI boot flash programming, UDP communication, TCP communication and a logic analyzer for remote debugging. All this in a single easy to use core.

The UDP and TCP interfaces are standard AXI4 Streams with status/setup signals.

SPI boot flash programming is done with FPGA Programmer.

The core is available for Xilinx 7 Series (Spartan, Artix, Kintex, Virtex, Zynq).

Signal Interface

| Name | Direction | Width | Remarks |

|---|---|---|---|

| Sys/Common | |||

| Clk | in | 1 | 125 MHz |

| Clk_Tx | in | 1 | 125 MHz RGMII Transmit clock |

| Reset | in | 1 | Active high |

| UseDHCP | in | 1 | '1' to use DHCP |

| IP_Addr | in | 32 | IP address if not using DHCP |

| IP_Ok | out | 1 | DHCP ready |

| TCP Basic Server | |||

| TCP0_Service | in | 16 | Service |

| TCP0_ServerPort | in | 16 | TCP local server port |

| TCP0_Connected | out | 1 | Client connected |

| TCP0_AllAcked | out | 1 | All outgoing data acked |

| TCP0_nTxFree | out | 16 | Number of free bytes in outgoing buffer |

| TCP0_nRxData | out | 16 | Number of bytes in receiving buffer |

| TCP0_TxData | in | 8 | Transmit data |

| TCP0_TxValid | in | 1 | Transmit data valid |

| TCP0_TxReady | out | 1 | Transmit data ready |

| TCP0_RxData | out | 8 | Receive data |

| TCP0_RxValid | out | 1 | Receive data valid |

| TCP0_RxReady | in | 1 | Receive data ready |

| MAC/RGMII | |||

| RGMII_TXC | out | 1 | |

| RGMII_TXD | out | 4 | |

| RGMII_TX_CTL | out | 1 | |

| RGMII_RXC | in | 1 | |

| RGMII_RXD | in | 4 | |

| RGMII_RX_CTL | in | 1 | |

| RGMII_MDC | out | 1 | |

| RGMII_MDIO | in/out | 1 | |

| SPI/Boot Control | |||

| SPI_CSn | out | 1 | Chip select |

| SPI_SCK | out | 1 | Serial clock |

| SPI_MOSI | out | 1 | Master out slave in |

| SPI_MISO | in | 1 | Master in slave out |

| Logic Analyzer | |||

| LA0_TrigIn | in | 1 | Trigger input |

| LA0_Clk | in | 1 | Clock |

| LA0_TrigOut | out | 1 | Trigger out |

| LA0_Signals | in | 32 | Signals |

| LA0_SampleEn | in | 1 | Sample enable |

| UDP Basic Server | |||

| UDP0_Reset | in | 1 | Reset interface, active high |

| UDP0_Service | in | 16 | Service |

| UDP0_ServerPort | in | 16 | UDP local server port |

| UDP0_Connected | out | 1 | Client connected |

| UDP0_OutIsEmpty | out | 1 | All outgoing data acked |

| UDP0_TxData | in | 8 | Transmit data |

| UDP0_TxValid | in | 1 | Transmit data valid |

| UDP0_TxReady | out | 1 | Transmit data ready |

| UDP0_TxLast | in | 1 | Transmit data last |

| UDP0_RxData | out | 8 | Receive data |

| UDP0_RxValid | out | 1 | Receive data valid |

| UDP0_RxReady | in | 1 | Receive data ready |

| UDP0_RxLast | out | 1 | Transmit data last |

Downloads

Copyright ©2021 FPGA-Cores.com.This HDL code and netlists are only free to use for non - commercial users and for evaluation purpose. Commercial use needs a commercial license.

The HDL code and netlists are distributed on an "AS IS" BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

VHDL Component: FC1004_RGMII.vhd

Verilog Module: FC1004_RGMII.vh

Xilinx 7 Series Netlist: FC1004_RGMII.edn