Description

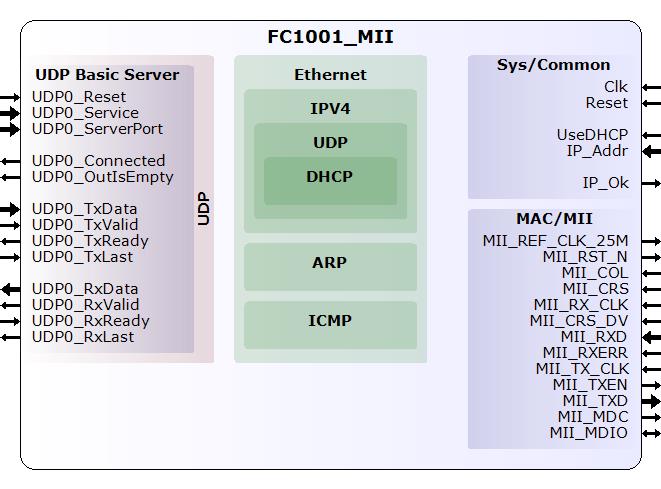

FC1001_MII contains all functions to add a FPGA to an Ethernet network with a Media Independent Interface, MII.

This is the smallest core with only the absolute necessary functions to enable UDP communication.

The UDP interface is a standard AXI Stream interface with status signals.

The core is available for Xilinx 7 Series.

Signal Interface

| Name | Direction | Width | Remarks |

|---|---|---|---|

| Sys/Common | |||

| Clk | in | 1 | 100 MHz |

| Reset | in | 1 | Active high |

| UseDHCP | in | 1 | '1' to use DHCP |

| IP_Addr | in | 32 | IP address if not using DHCP |

| IP_Ok | out | 1 | DHCP ready |

| MAC/MII | |||

| MII_REF_CLK_25M | out | 1 | MII continous 25 MHz reference clock |

| MII_RST_N | out | 1 | Phy reset, active low |

| MII_COL | in | 1 | Collision detect |

| MII_CRS | in | 1 | Carrier sense |

| MII_RX_CLK | in | 1 | Receive clock |

| MII_CRS_DV | in | 1 | Receive data valid |

| MII_RXD | in | 4 | Receive data |

| MII_RXERR | in | 1 | Receive error |

| MII_TX_CLK | in | 1 | Transmit clock |

| MII_TXEN | out | 1 | Transmit enable |

| MII_TXD | out | 4 | Transmit data |

| MII_MDC | out | 1 | Management clock |

| MII_MDIO | in/out | 1 | Management data |

| UDP Basic Server | |||

| UDP0_Reset | in | 1 | Reset interface, active high |

| UDP0_Service | in | 16 | Service |

| UDP0_ServerPort | in | 16 | UDP local server port |

| UDP0_Connected | out | 1 | Client connected |

| UDP0_OutIsEmpty | out | 1 | All outgoing data acked |

| UDP0_TxData | in | 8 | Transmit data |

| UDP0_TxValid | in | 1 | Transmit data valid |

| UDP0_TxReady | out | 1 | Transmit data ready |

| UDP0_TxLast | in | 1 | Transmit data last |

| UDP0_RxData | out | 8 | Receive data |

| UDP0_RxValid | out | 1 | Receive data valid |

| UDP0_RxReady | in | 1 | Receive data ready |

| UDP0_RxLast | out | 1 | Transmit data last |

Downloads

Copyright ©2018 FPGA-Cores.com.This HDL code and netlists are only free to use for non - commercial users and for evaluation purpose. Commercial use needs a commercial license.

The HDL code and netlists are distributed on an "AS IS" BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

VHDL Component: FC1001_MII.vhd

Verilog Module: FC1001_MII.vh

Xilinx 7 Series Netlist: FC1001_MII.edn

Xilinx Spartan 6 Netlist: FC1001_MII.ngc